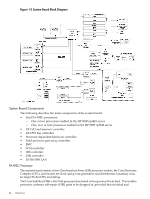

HP rp3440 User Service Guide, Sixth Edition - HP 9000 rp3410/rp3440 - Page 28

Field Programmable Gate Array, BMC, SCSI Controller

|

View all HP rp3440 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 28 highlights

• 16-bit PDH bus with reserved address space for the following: - Flash memory - Nonvolatile memory - Scratch RAM - Real-time clock - UARTs - External registers - Firmware read/writable registers - Two general purpose 32-bit registers - Semaphore registers - Monarch selection registers - Test and reset register • Reset and INIT generation Field Programmable Gate Array The Field Programmable Gate array (FPGA) provides ACPI and LPC support for the PDH bus and provides these features: • ACPI 2.0 interface • LPC bus interface to support BMC • Decoding logic for PDH devices BMC The BMC supports the industry-standard Intelligent Platform Management Interface (IPMI) specification. This specification describes the management features that have been built into the system board. These features include: diagnostics (both local and remote), console support, configuration management, hardware management and troubleshooting. The BMC provides the following: • Compliance with IPMI 1.0 • Tachometer inputs for fan speed monitoring • Pulse width modulator outputs for fan speed control • Push-button inputs for front panel buttons and switches • One serial port, multiplexed with the system console port • Remote access and intelligent chassis management bus (ICMB) support • Three I2C master/slave ports (one of the ports is used for intelligent platform management bus (IPMB) • Low Pin Count (LPC) bus provides access to three Keyboard Controller Style (KCS) and one-Block Transfer (BT) interface • 32-bit ARM7 RISC processor • 160-pin Low Profile Flat Pack (LQFP) package • Firmware is provided for the following interfaces: - IPMI - IPMB SCSI Controller The SCSI controller is a LSI Logic 53C1030 chip. This chip is fully compliant with the SCSI Peripheral Interface-4 Specification (SPI-4). It has two independent SCSI channels supporting devices at speeds up to 320 MB/seconds each. The 53C1030 adheres to the PCI-X addendum, to the PCI Local Specification, and is hard-wired to PCI ID 1 which corresponds to bit 17 of the PCI AD bus. 28 Overview