HP Visualize J5000 hp Visualize J5000, J7000 workstations service handbook (a4 - Page 60

Table 3-1. Chassis Codes for J5000 and J7000 Workstations, Ostat, Message

|

View all HP Visualize J5000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 60 highlights

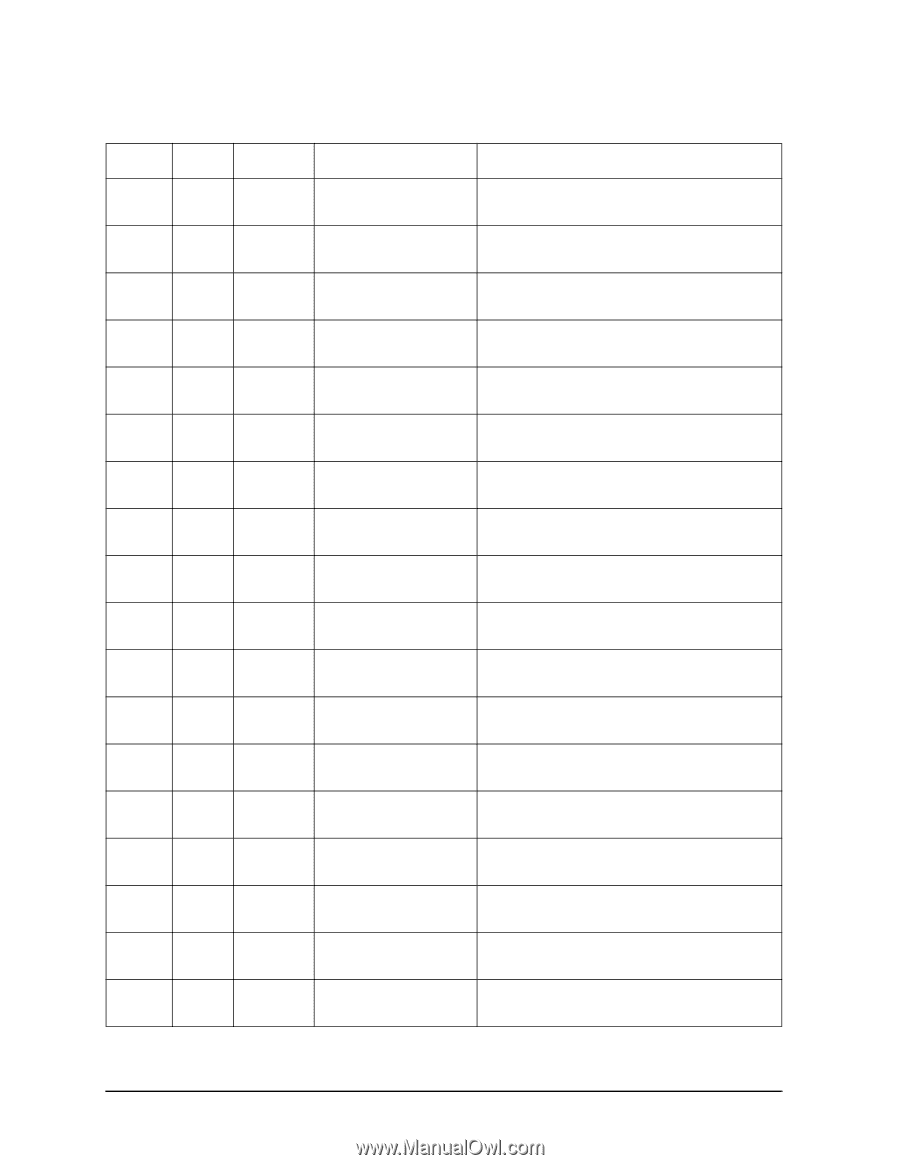

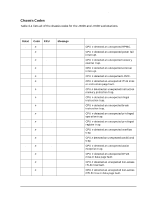

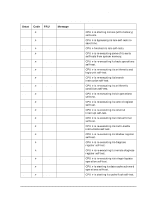

Troubleshooting Identifying LCD-Indicated Conditions Table 3-1. Chassis Codes for J5000 and J7000 Workstations Ostat FLT FLT FLT FLT FLT FLT FLT FLT FLT FLT FLT FLT TST TST TST TST TST TST Code FRU 1n12 SYS BD 1n13 SYS BD 1n14 SYS BD 1n15 SYS BD 1n16 SYS BD 1n17 SYS BD 1n18 SYS BD 1n19 SYS BD 1n1A SYS BD 1n1B SYS BD 1n1C SYS BD 1n1D SYS BD 1n20 SYS BD 1n21 SYS BD 1n22 SYS BD 1n23 SYS BD 1n24 SYS BD 1n25 SYS BD Message Description data mem prot tr CPU n detected an unexpected data memory protection trap. data mem brk trp CPU n detected an unexpected data memory break trap. TLB dirty bit tr CPU n detected an unexpected TLB dirty bit trap. page refrnce trp CPU n detected an unexpected page reference trap. assist emul trap CPU n detected an unexpected assist emulation trap. hi-priv xfer trp CPU n detected an unexpected higher-privilege transfer trap. lo-priv xfer trp CPU n detected an unexpected lower-privilege transfer trap. taken branch trp CPU n detected an unexpected taken-branch trap. data mem acc rts CPU n detected an unexpected data memory access rights trap. data mem prot ID CPU n detected an unexpected data memory protection ID trap. unalign data ref CPU n detected an unexpected unaligned data reference trap. perf mon intrrpt CPU n detected an unexpected performance monitor interrupt. CPUn basic test CPU n is starting its basic operations self-test. CPUn alu test CPU n is starting its arithmetic and logical unit self-test. CPUn branch test CPU n is starting its branch instruction self-test. CPUn arith cond CPU n is starting its arthimetic condition self-test. CPUn bit opers CPU n is starting its bit operation instruction self-test. CPUn cntrl regs CPU n is starting its control register self-test. 56 Chapter 3