HP Visualize J5000 hp Visualize J5000, J7000 workstations service handbook (a4 - Page 64

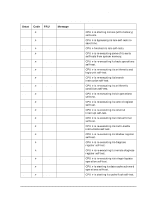

Invoke LDB, Check LANIC address.

|

View all HP Visualize J5000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 64 highlights

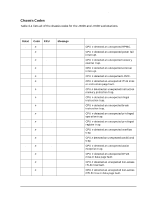

Troubleshooting Identifying LCD-Indicated Conditions Table 3-1. Chassis Codes for J5000 and J7000 Workstations Ostat INI FLT WRN TST WRN FLT TST WRN FLT INI TST INI FLT FLT TST INI FLT FLT FLT FLT Code FRU 3n07 SYS BD 3n09 SYS BD 3n1A SYS BD 3n1B SYS BD 3n1B SYS BD 3n1B SYS BD 3n1C 3n1C 3n1C 3n2s SYS BD SYS BD SYS BD SYS BD 3nBC IO BD 3nBC 3nBC SYS BD IO BD 3nCD IO BD 3nCD SYS BD 3nCD SYS BD 3nCD SYS BD 3nEC SYS BD 3nF4 SYS BD 3nFC SYS BD Message Description CPUn invoke LDB CPU n is starting the low-level debugger. bad sys mde byte CPU n detected an unsupported system mode. hversion mismtch Stable store hardware version doesn't match system. chck model strng Check model string with version in stable store. model str msmtch Model string doesn't match that in stable store. fatal model str Error reading model string from stable store. test software ID Check LANIC address. update sw ID Update LANIC address. update sw ID err Error updating LANIC address. Invoke LDB: s CPU n is awaiting the low-level debugger for s more seconds. test sys clocks CPU n is verifying processor clocks with the real-time clock. init sys clocks CPU n has initialized the processor clocks. RTC tick timeout The real-time clock is ticking too slowly or not at all. RTC tick timeout The real time clock is ticking too slowly or not at all. check defaults CPU n is initializing stable store values to system defaults. init defaults CPU n finished initializing stable store values. init EEPROM err CPU n detected an error writing to stable store. bad sys config CPU n detected an illegal CPU board configuration. EEPROM boot limt CPU n detected a fatal error writing the EEPROM. bad sys bd id CPU n cannot identify CPU board. 60 Chapter 3