HP Visualize J5000 hp Visualize J5000, J7000 workstations service handbook (a4 - Page 65

Description, lst itimer

|

View all HP Visualize J5000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 65 highlights

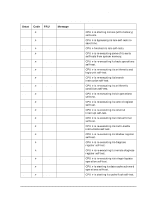

Troubleshooting Identifying LCD-Indicated Conditions Table 3-1. Chassis Codes for J5000 and J7000 Workstations Ostat TST WRN TST TST TST TST TST TST TST TST TST TST TST TST TST TST TST TST TST Code FRU 4n00 SYS BD 4n01 SYS BD 4n0E 4n20 SYS BD SYS BD 4n21 SYS BD 4n22 SYS BD 4n23 SYS BD 4n24 SYS BD 4n25 SYS BD 4n26 SYS BD 4n27 SYS BD 4n28 SYS BD 4n29 SYS BD 4n2A SYS BD 4n2B SYS BD 4n2C SYS BD 4n2D SYS BD 4n30 SYS BD 4n40 SYS BD Message Description CPUn start lst CPU n is starting its late (with memory) self-tests. CPUn skip lst CPU n is bypassing its late self-tests to save time. CPUn exit lst CPU n finished its late self-tests. CPUn lst erly st CPU n is re-executing some of its early self-tests from system memory. CPUn lst basic CPU n is re-executing its basic operations self-test. CPUn lst alu CPU n is re-executing its arithmetic and logic unit self-test. CPUn lst branch CPU n is re-executing its branch instruction self-test. CPUn lst arth cd CPU n is re-executing its arithmetic conditions self-test. CPUn lst bit ops CPU n is re-executing its bit operations self-test. CPUn lst ctl reg CPU n is re-executing its control register self-test. CPUn lst ext int CPU n is re-executing its external interrupt self-test. CPUn lst itimer CPU n is re-executing its interval timer self-test. CPUn lst mltimed CPU n is re-executing its multi-media instructions self-test. CPUn lst shadow CPU n is re-executing its shadow register self-test. CPUn lst dg regs CPU n is re-executing its diagnose register self-test. CPUn lst rdrs CPU n is re-executing its remote diagnose register self-test. CPUn lst bypass CPU n is re-executing its integer bypass operation self-test. CPUn cache byte CPU n is starting its data cache sub-word operations self-test. CPUn cache flush CPU n is starting its cache flush self-test. Chapter 3 61