HP Visualize J5000 hp Visualize J5000, J7000 workstations service handbook (a4 - Page 62

Identifying LCD-Indicated Conditions, PDC_PROC halted CPU

|

View all HP Visualize J5000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 62 highlights

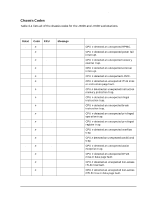

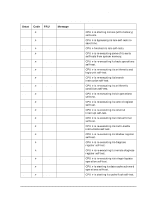

Troubleshooting Identifying LCD-Indicated Conditions Table 3-1. Chassis Codes for J5000 and J7000 Workstations Ostat TST FLT FLT FLT INI WRN WRN FLT WRN WRN WRN INI INI FLT TST FLT FLT TST TST TST FLT TST Code FRU 1nB2 SYS BD 1nBA 1nBB 1nBF 1nCA SYS BD SYS BD SYS BD SYS BD 1nCD 1nCE 1nCF 1mDs SYS BD SYS BD SYS BD SYS BD 1nEF SYS BD 1mFs 1nFC SYS BD SYS BD 1nFD 1nFF 2n20 SYS BD SYS BD SYS BD 2n25 SYS BD 2n26 SYS BD 2n30 SYS BD 2n40 SYS BD 2n50 SYS BD 2n51 SYS BD 2n70 SYS BD Message Description CPUn TLB trans CPU n is starting its TLB translation self-test. monarch CPU fail The monarch CPU failed. bad CPUn number The CPU identifier was out of range. CPUn halt boot Bootstrap failure--machine halted. CPUn sys bus arb Monarch CPU is initializing the system bus arbitration. CPUn deconfig CPU n deconfigured itself. CPUn extinguish PDC_PROC halted CPU n. slaven failed Slave CPU n failed self-test. slaves deconfig Monarch CPU m deconfigured slave CPU s. CPUn slftst warn CPU n detected a non-fatal error during its self-tests. monm stop slaves Monarch CPU m halted slave CPU s. CPUn sync'ing CPU n is synchronizing with the rest of the system. CPUn stat wd tst CPU n is testing the system status word. monarchn selftst Monarch CPU n failed self-test. CPUn icache RAM CPU n is starting its instruction cache RAM self-test. CPUn ic ld d err CPU n detected a data error during data cache load. CPUn ic ld t err CPU n detected a tag error during data cache load. CPUn icache tag CPU n is starting its instruction cache tag self-test. CPUn icache par CPU n is starting its instruction cache parity detection self-test. CPUn dc stor que CPU n is starting its data cache store queue self-test. CPUn dc st q err CPU n detected an error during its data cache store queue self-test. CPUn dcache RAM CPU n is starting its data cache RAM self-test. 58 Chapter 3