HP Visualize J5000 hp Visualize J5000, J7000 workstations service handbook (a4 - Page 66

mem plt upd fail, init mem tables

|

View all HP Visualize J5000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 66 highlights

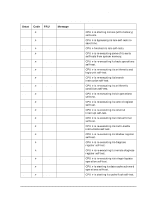

Troubleshooting Identifying LCD-Indicated Conditions Table 3-1. Chassis Codes for J5000 and J7000 Workstations Ostat TST TST FLT FLT FLT FLT FLT FLT FLT FLT INI INI FLT FLT TST WRN FLT FLT TST Code FRU 4n50 SYS BD 4n60 SYS BD 5n00 SYS BD 5n02 SYS BD 5n04 SYS BD 5n07 SYS BD 5n08 SYS BD 5n0A SYS BD 5n0B SYS BD 5n0C SYS BD 7000 7002 7004 7005 7010 7011 7012 DIMM SYS BD SYS BD DIMM DIMM DIMM DIMM 7013 DIMM 7016 DIMM Message Description CPUn icache miss CPU n is starting its instruction cache miss self-test. CPUn dcache miss CPU n is starting its data cache miss self-test. unknown bus err CPU n detected an unknown error on the system bus (Runway). path err assertd CPU n detected a path error on the system bus (Runway). data parity err CPU n detected a data, address, or control parity error on the system bus (Runway). Runway dir error CPU n detected a directed error on the system bus (Runway). Runway broad err CPU n detected a broadcast error on the system bus (Runway). illegal response CPU n received data that did not match any outstanding data request. bus timeout CPU n timed out before receiving requested data. The responder is logged in the system responder address. CPU sync failure CPU n's synchronizer detected a rule violation on the system bus (Runway). start DIMM scan Start looking for installed DIMMs. init mem tables Initialize memory data structures. mem plt upd fail Error updating memory platform data. insufficient mem Insufficient memory detected to continue. check DIMM order Start memory DIMM order check. skip DIMM ord ck Bypass memory DIMM order check. DIMM order error Memory DIMMs are not in the proper order. DIMM order error Memory DIMMs are not in the proper order. As a result, the system cannot access one or more DIMMs and has deallocated all inaccessible DIMMs. DIMM pair check Start memory DIMM pair check (DIMMs in a pair (e.g. 0a/0b) must match in J7000). 62 Chapter 3