HP Visualize J5000 hp Visualize J5000, J7000 workstations service handbook (a4 - Page 61

Ostat, Message, Identifying LCD-Indicated Conditions

|

View all HP Visualize J5000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 61 highlights

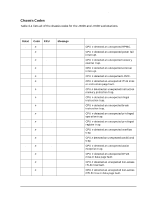

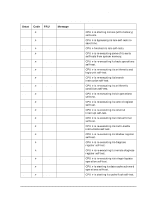

Troubleshooting Identifying LCD-Indicated Conditions Table 3-1. Chassis Codes for J5000 and J7000 Workstations Ostat TST TST TST TST TST TST TST TST WRN FLT INI TST TST TST TST TST TST TST TST Code FRU 1n26 SYS BD 1n27 SYS BD 1n28 SYS BD 1n29 SYS BD 1n2A SYS BD 1n2B SYS BD 1n2C SYS BD 1n30 SYS BD 1n31 SYS BD 1n32 SYS BD 1n3C 1n3E 1nA0 SYS BD SYS BD SYS BD 1nA1 SYS BD 1nA2 SYS BD 1nA3 SYS BD 1nA4 SYS BD 1nA5 SYS BD 1nB1 SYS BD Message Description CPUn ext intrpt CPU n is starting its external interrupt self-test. CPUn itimer test CPU n is starting its interval timer self-test. CPUn multi-media CPU n is starting its multi-media instructions self-test. CPUn shadow reg CPU n is starting its shadow register self-test. CPUn diagnse reg CPU n is starting its diagnose register self-test. CPUn rdr test CPU n is starting its remote diagnose register self-test. CPUn bypass test CPU n is starting its integer bypass operation self-test. CPUn start est CPU n is starting its early (pre-memory) self-tests. CPUn skip est CPU n is bypassing its early self-tests to save time. CPUn bad tst mod CPU n detected an unsupported system mode. CPUn initialize CPU n is initializing after self-tests. CPUn exit est CPU n finished its early self-tests. CPUn fpu tests CPU n is starting its floating-point unit self-tests. CPUn fpu reg tst CPU n is starting its floating-point register self-test. CPUn fpu inst CPU n is starting its floating-point instruction self-test. CPUn fpu traps CPU n is starting its floating-point trap self-test. CPUn fpu misc CPU n is starting its floating-point miscellaneous operations self-test. CPUn fpu bypass CPU n is starting its floating-point bypassing self-test. CPUn TLB RAM tst CPU n is starting its TLB register self-test. Chapter 3 57