Dell PowerEdge T605 Hardware Owner's Manual (PDF) - Page 48

CPU Information Screen, CPU Information

|

View all Dell PowerEdge T605 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 48 highlights

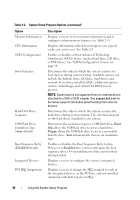

Table 2-3. Memory Information Screen (continued) Option Redundant Memory (Disabled default) Node Interleaving Memory Optimizer Technology (Enabled default) Description Enables or disables the redundant memory feature. When set to Spare Mode, the first rank of memory on each DIMM is reserved for memory sparing (see "Memory Sparing Support" on page 128). Redundant memory feature is disabled if the Node Interleaving field is enabled. If this field is enabled, memory interleaving is supported if a symmetric memory configuration is installed. If this field is set to disabled (the default), the system can support Non-Uniform Memory architecture (NUMA) (asymmetric) memory configurations. NOTE: The Node Interleaving field must be set to Disabled when using the redundant memory feature. Sets the behavior of the two DRAM controllers for memory optimization. When set to Enabled, the two controllers run in parallel 64-bit mode for improved memory performance (running single-bit ECC). When set to Disabled, the controllers are joined in 128-bit mode running multi-bit Advanced ECC, but memory performance is not optimized. CPU Information Screen Table 2-4 lists the options and descriptions for the information fields that appear on the CPU Information screen. Table 2-4. CPU Information Screen Option 64-bit Core Speed Bus Speed Description Specifies if the installed processors support 64-bit extensions. Displays the clock speed of the processors. Displays the bus speed of the processors. 48 Using the System Setup Program