Intel 925 Data Sheet - Page 101

DMIPVCCAP2-DMI Port VC Capability Register 2, DMIPVCCTL-DMI Port VC Control

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

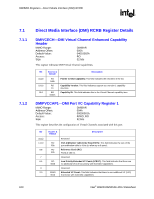

Page 101 highlights

DMIBAR Registers-Direct Media Interface (DMI) RCRB R 7.1.3 7.1.4 DMIPVCCAP2-DMI Port VC Capability Register 2 MMIO Range: Address Offset: Default Value: Access: Size: DMIBAR 008h 00000001h RO 32 bits This register describes the configuration of Virtual Channels associated with this port. Bit 31:24 23:8 7:0 Access & Default Description RO VC Arbitration Table Offset (ATO): This field indicates that no table is present 00h for VC arbitration since it is fixed. Reserved RO VC Arbitration Capability: This field indicates that the VC arbitration is fixed in 01h the root complex. VC1 is highest priority and VC0 is lowest priority. DMIPVCCTL-DMI Port VC Control MMIO Range: Address Offset: Default Value: Access: Size: DMIBAR 00Ch 00000000h R/W, RO 16 bits Bit Access & Default Description 15:4 Reserved 3:1 R/W VC Arbitration Select: This field indicates which VC should be programmed in 000b the VC arbitration table. The root complex takes no action on the setting of this field since there is no arbitration table. 0 RO Load VC Arbitration Table (LAT): This field indicates that the table programmed 0b should be loaded into the VC arbitration table. This bit is defined as read/write with always returning 0 on reads. Intel® 82925X/82925XE MCH Datasheet 101