Intel 925 Data Sheet - Page 97

EPLE2A-EP Link Entry 2 Address

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 97 highlights

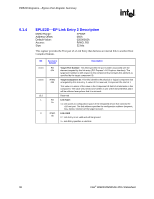

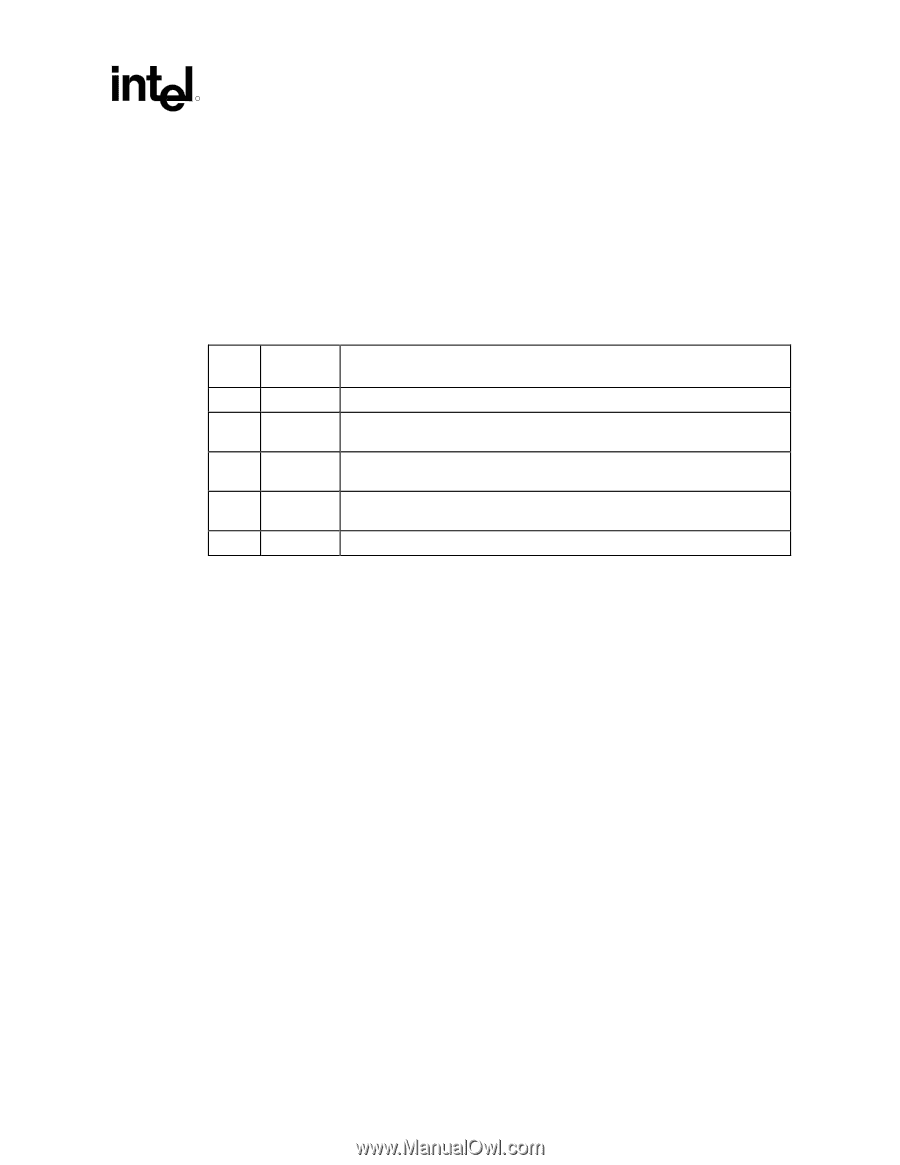

EPBAR Registers-Egress Port Register Summary R 6.1.5 EPLE2A-EP Link Entry 2 Address MMIO Range: Address Offset: Default Value: Access: Size: EPBAR 068h 0000000000008000h RO 64 bits This register provides the second part of a Link Entry that declares an internal link to another Root Complex Element. Bit 63:28 27:20 19:15 14:12 11:0 Access & Default RO 00h RO 0 0001b RO 000b Description Reserved Bus Number Device Number: Target for this link is PCI Express* x16 port (Device 1). Function Number Reserved § Intel® 82925X/82925XE MCH Datasheet 97

EPBAR Registers—Egress Port Register Summary

R

Intel

®

82925X/82925XE MCH Datasheet

97

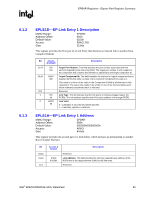

6.1.5

EPLE2A—EP Link Entry 2 Address

MMIO Range:

EPBAR

Address Offset:

068h

Default Value:

0000000000008000h

Access:

RO

Size:

64 bits

This register provides the second part of a Link Entry that declares an internal link to another

Root Complex Element.

Bit

Access &

Default

Description

63:28

Reserved

27:20

RO

00h

Bus Number

19:15

RO

0 0001b

Device Number:

Target for this link is PCI Express* x16 port (Device 1).

14:12

RO

000b

Function Number

11:0

Reserved

§