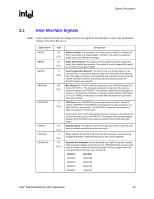

Intel 925 Data Sheet - Page 25

Signal Name, Description, Host Reference Voltage Reference

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 25 highlights

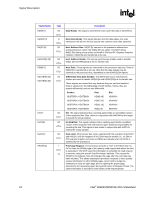

Signal Description R Signal Name HREQ[4:0]# HTRDY# HRS[2:0]# BSEL[2:0] HRCOMP HSCOMP HSWING HVREF Type I/O GTL+ 2x O GTL+ O GTL+ I CMOS I/O CMOS I/O CMOS I A I A Description Host Request Command: These signals define the attributes of the request. HREQ[4:0]# are transferred at 2x rate. They are asserted by the requesting agent during both halves of Request Phase. In the first half the signals define the transaction type to a level of detail that is sufficient to begin a snoop request. In the second half the signals carry additional information to define the complete transaction type. The transactions supported by the MCH Host Bridge are defined in the Host Interface section of this document. Host Target Ready: This signal indicates that the target of the processor transaction is able to enter the data transfer phase. Response Signals: These signals indicate the type of response as shown below: 000 = Response type 001 = Idle state 010 = Retry response 011 = Deferred response 100 = Reserved (not driven by MCH) 101 = Hard Failure (not driven by MCH) 110 = No data response 111 = Implicit Writeback 111 = Normal data response Bus Speed Select: At the de-assertion of RSTIN#, the value sampled on these pins determines the expected frequency of the bus. Host RCOMP: Used to calibrate the Host GTL+ I/O buffers. This signal is powered by the Host Interface termination rail (VTT). Slew Rate Compensation: Compensation for the Host Interface. Host Voltage Swing: This signal provides the reference voltage used by FSB RCOMP circuits. HSWING is used for the signals handled by HRCOMP. Host Reference Voltage Reference: Voltage input for the data, address, and common clock signals of the Host GTL interface. Intel® 82925X/82925XE MCH Datasheet 25