Intel 925 Data Sheet - Page 222

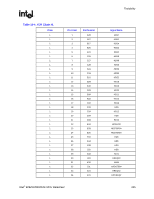

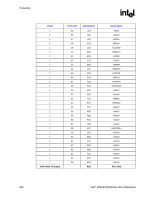

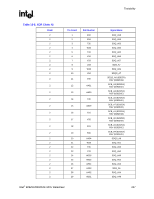

XOR Test Mode Initialization, XOR Chain Definition, XOR Chains, Table 13-2. XOR Chain Outputs

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 222 highlights

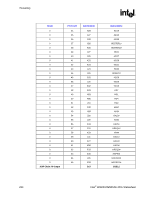

Testability R 13.2 XOR Test Mode Initialization XOR test mode can be entered by pulling reserved ballout RSV (located at F15) and MTYPE low through the de-assertion of external reset (RSTIN#). It is recommended that customers use the following sequence. After power up, hold PWROK, PCIRST#, and reserved ballout RSV (located at F15) and MTYPE low and start external clocks. After 20 cycles, pull PWROK high. After 15 clocks, deassert PCIRST# (pull it high). Release reserved ballout RSV (located at F15) and MTYPE. No external drive. Allow the clocks to run for an additional 32 clocks. Begin testing the XOR chains. 13.3 XOR Chain Definition The 82925X/82925XE MCH has 10 XOR chains. The XOR chain outputs are driven out on the following output pins. During full-width testing, XOR chain outputs will be visible on both pins. For example xor_out0 will be visible on BSEL2. Table 13-2. XOR Chain Outputs XOR Chain xor_out0 xor_out1 xor_out2 xor_out3 xor_out4 xor_out5 xor_out6 xor_out7 xor_out8 xor_out9 Output Pins BSEL2 RSV RSV MTYPE RSV RSV RSV RSV BSEL1 BSEL0 Coordinate Location D17 M16 F15 C15 A16 B15 C14 K15 E15 H16 13.4 XOR Chains The following tables show the XOR chains. The last section in this chapter has a pin exclusion list. The chain files are golden, if there is a pin missing from the chain files and exclusion list, it should be added to the exclusion list. 222 Intel® 82925X/82925XE MCH Datasheet