Intel 925 Data Sheet - Page 155

LE1A-Link Entry 1 Address D1:F0, PEGSSTS-PCI Express*-G Sequence Status D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 155 highlights

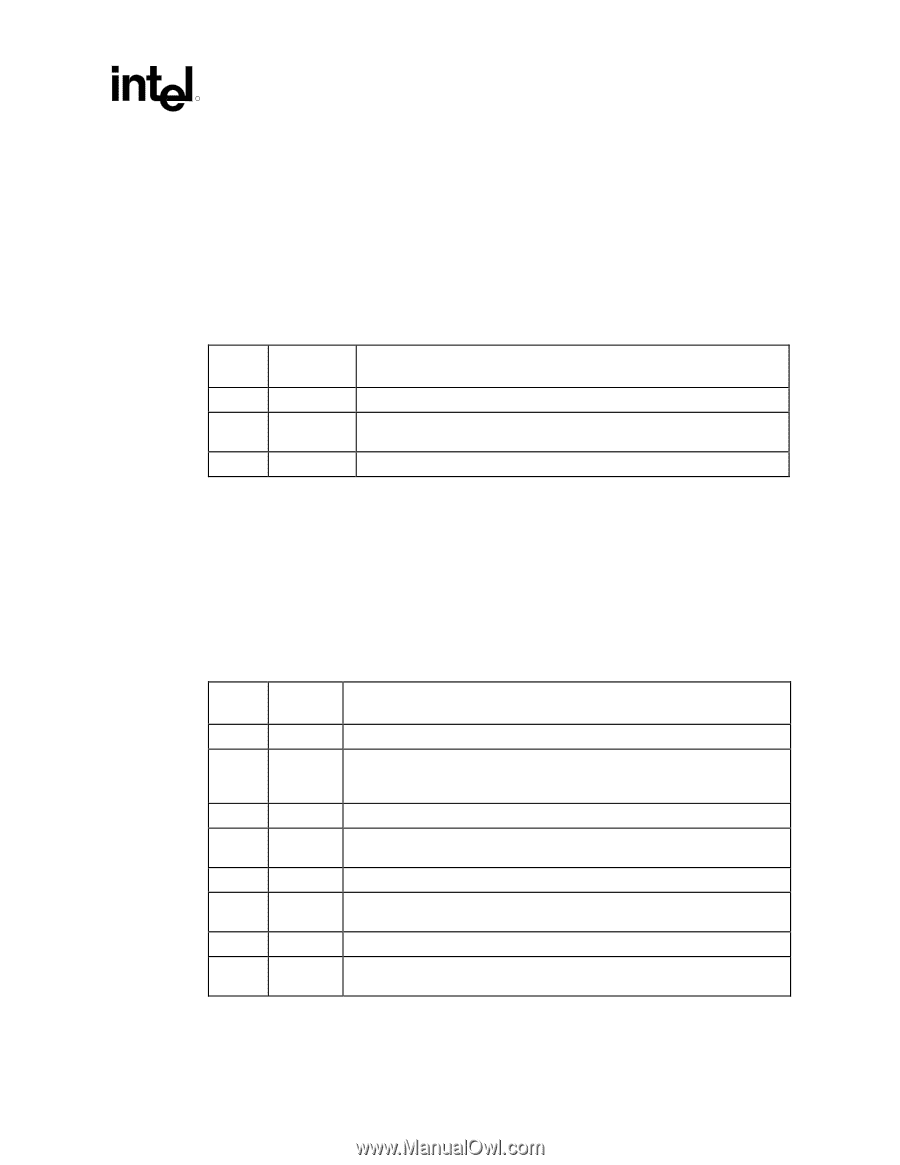

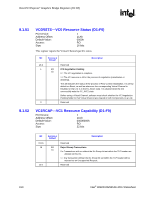

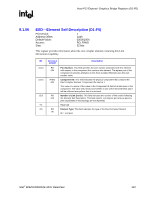

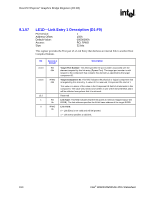

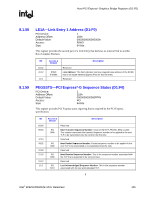

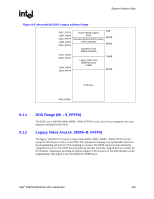

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.58 LE1A-Link Entry 1 Address (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 158h 0000000000000000h R/WO 64 bits This register provides the second part of a Link Entry that declares an internal link to another Root Complex Element. Bit 63:32 31:12 11:0 Access & Default R/WO 0 0000h Description Reserved Link Address: This field indicates memory-mapped base address of the RCRB that is the target element (Egress Port) for this link entry. Reserved 8.1.59 PEGSSTS-PCI Express*-G Sequence Status (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 218h 0000000000000FFFh RO 64 bits This register provides PCI Express status reporting that is required by the PCI Express specification. Bit 63:60 59:48 47:44 43:32 31:28 27:16 15:12 11:0 Access & Default Description RO 000h RO 000h RO 000h RO FFFh Reserved Next Transmit Sequence Number: Value of the NXT_TRANS_SEQ counter. This counter represents the transmit Sequence number to be applied to the next TLP to be transmitted onto the Link for the first time. Reserved Next Packet Sequence Number: Packet sequence number to be applied to the next TLP to be transmitted or re-transmitted onto the Link. Reserved Next Receive Sequence Number: This is the sequence number associated with the TLP that is expected to be received next. Reserved Last Acknowledged Sequence Number: This is the sequence number associated with the last acknowledged TLP. § Intel® 82925X/82925XE MCH Datasheet 155