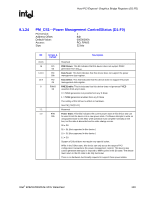

Intel 925 Data Sheet - Page 132

MC-Message Control D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

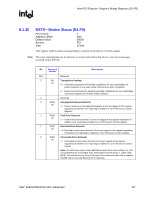

Page 132 highlights

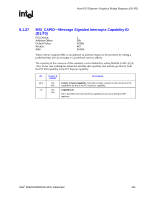

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.28 MC-Message Control (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 92h 0000h RO, R/W 16 bits System software can modify bits in this register, but the device is prohibited from doing so. If the device writes the same message multiple times, only one of those messages is guaranteed to be serviced. If all of them must be serviced, the device must not generate the same message again until the driver services the earlier one. Bit Access & Default Description 15:8 Reserved 7 RO 64-bit Address Capable: Hardwired to 0 to indicate that the function does not 0b implement the upper 32 bits of the Message Address register and is incapable of generating a 64-bit memory address. 6:4 R/W Multiple Message Enable (MME): System software programs this field to 000b indicate the actual number of messages allocated to this device. This number will be equal to or less than the number actually requested. 000 = 1 message allocated 001-111 = Reserved 3:1 RO Multiple Message Capable (MMC): System software reads this field to 000b determine the number of messages being requested by this device. 000 = 1 message requested 001-111 = Reserved 0 R/W MSI Enable (MSIEN) Controls the ability of this device to generate MSIs. 0b 0 = MSI will not be generated. 1 = MSI will be generated when we receive PME or HotPlug messages. INTA will not be generated and INTA Status (PCISTS1[3]) will not be set. 132 Intel® 82925X/82925XE MCH Datasheet