Intel 925 Data Sheet - Page 40

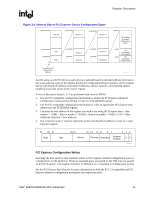

PCI Express* Enhanced Configuration Mechanism

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 40 highlights

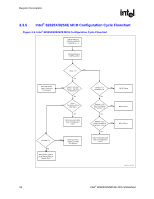

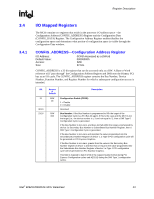

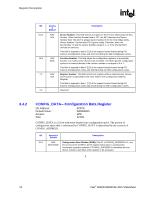

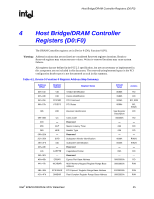

Register Description R Figure 3-3. DMI Type 1 Configuration Address Translation 31 30 1 Reserved Configuration Address 24 23 Bus Number 16 15 11 10 87 21 0 Device Number Function Double Word XX 3.3.4 31 30 1 OCFBh Reserved DMI Type 1 Configuration Address Extension 24 23 OCFAh Bus Number OCF9h 16 15 11 10 OCF8h 87 21 0 Device Number Function Double Word 00 DMI_Typ1_Config PCI Express* Enhanced Configuration Mechanism PCI Express extends the configuration space to 4096 bytes per device/function as compared to 256 bytes allowed by PCI Specification, Revision 2.3. PCI Express configuration space is divided into a PCI 2.3 compatible region that consists of the first 256B of a logical device's configuration space and a PCI Express extended region that consists of the remaining configuration space. The PCI compatible region can be accessed using either the mechanism defined in the previous section or using the enhanced PCI Express configuration access mechanism described in this section. The extended configuration registers may only be accessed using the enhanced PCI Express configuration access mechanism. To maintain compatibility with PCI configuration addressing mechanisms, system software must access the extended configuration space using 32bit operations (32-bit aligned) only. These 32-bit operations include byte enables allowing only appropriate bytes within the DWord to be accessed. Locked transactions to the PCI Express memory mapped configuration address space are not supported. All changes made using either access mechanism are equivalent. The enhanced PCI Express configuration access mechanism uses a flat memory-mapped address space to access device configuration registers. This address space is reported by the system firmware to the operating system. The PCIEXBAR register defines the base address for the 256-MB block of addresses below top of addressable memory (currently 4 GB) for the configuration space associated with all devices and functions that are potentially a part of the PCI Express root complex hierarchy. The PCI Express Configuration Transaction Header includes an additional 4 bits (Extended Register Address[3:0]) between the Function Number and Register Address fields to provide indexing into the 4 KB of configuration space allocated to each potential device. For PCI Compatible Configuration Requests, the Extended Register Address field must be all zeros. 40 Intel® 82925X/82925XE MCH Datasheet