Intel 925 Data Sheet - Page 187

Signal Groups, PCI Express, Analog, HVCMOS, SSTL-1.8

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

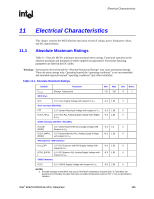

Page 187 highlights

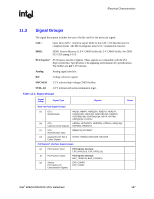

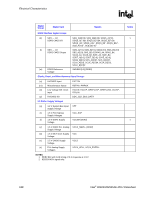

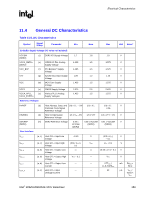

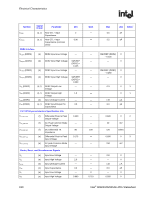

Electrical Characteristics R 11.3 Signal Groups The signal description includes the type of buffer used for the particular signal: GTL+ Open Drain GTL+ interface signal. Refer to the GTL+ I/O Specification for complete details. The MCH integrates most GTL+ termination resistors. DDR2 DDR2 System Memory (1.8 V CMOS buffers)(1.9 V CMOS buffers for DDR 533 CAS timing 3-3-3) PCI Express* PCI Express Interface Signals. These signals are compatible with the PCI Express Interface Specification 1.0a signaling environment AC specifications. The buffers are not 3.3V tolerant. Analog Analog signal interface. Ref Voltage reference signal. HVCMOS 2.5 V tolerant high voltage CMOS buffers. SSTL-1.8 1.8 V tolerant stub series termination logic. Table 11-4. Signal Groups Signal Group Signal Type Signals Notes Host Interface Signal Groups (a) GTL+ Input/Outputs HADS#, HBNR#, HBREQ0#, HDBSY#, HDRDY#, HDINV[3:0]#, HA[31:3]#, HADSTB[1:0]#, HD[63:0], HDSTBP[3:0]#, HDSTBN[3:0]#, HHIT#, HHITM#, HREQ[4:0]#, HLOCK# (b) GTL+ HBPRI#, HCPURST#, HDEFER#, HTRDY#, HRS[2:0]#, Common Clock Outputs HDPWR#, HEDRDY# (c) GTL+ Asynchronous Input BSEL[2:0], HPCREQ# (d) Analog Host I/F Ref & HVREF, HSWING HRCOMP, HSCOMP Comp. Signals PCI Express* Interface Signal Groups (e) PCI Express* Input PCI Express Interface: EXP_RXN(15:0), EXP_RXP(15:0), (f) PCI Express Output PCI Express Interface: EXP_TXN(15:0), EXP_TXP(15:0) (g) Analog EXP_COMP0 PCI Express I/F EXP_COMPI Compensation Signals Intel® 82925X/82925XE MCH Datasheet 187