Intel 925 Data Sheet - Page 34

Table 2-5. Clocking Reset and S3 States, Interface, Signal Name, State During, RSTIN, Assertion

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 34 highlights

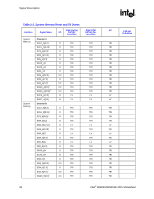

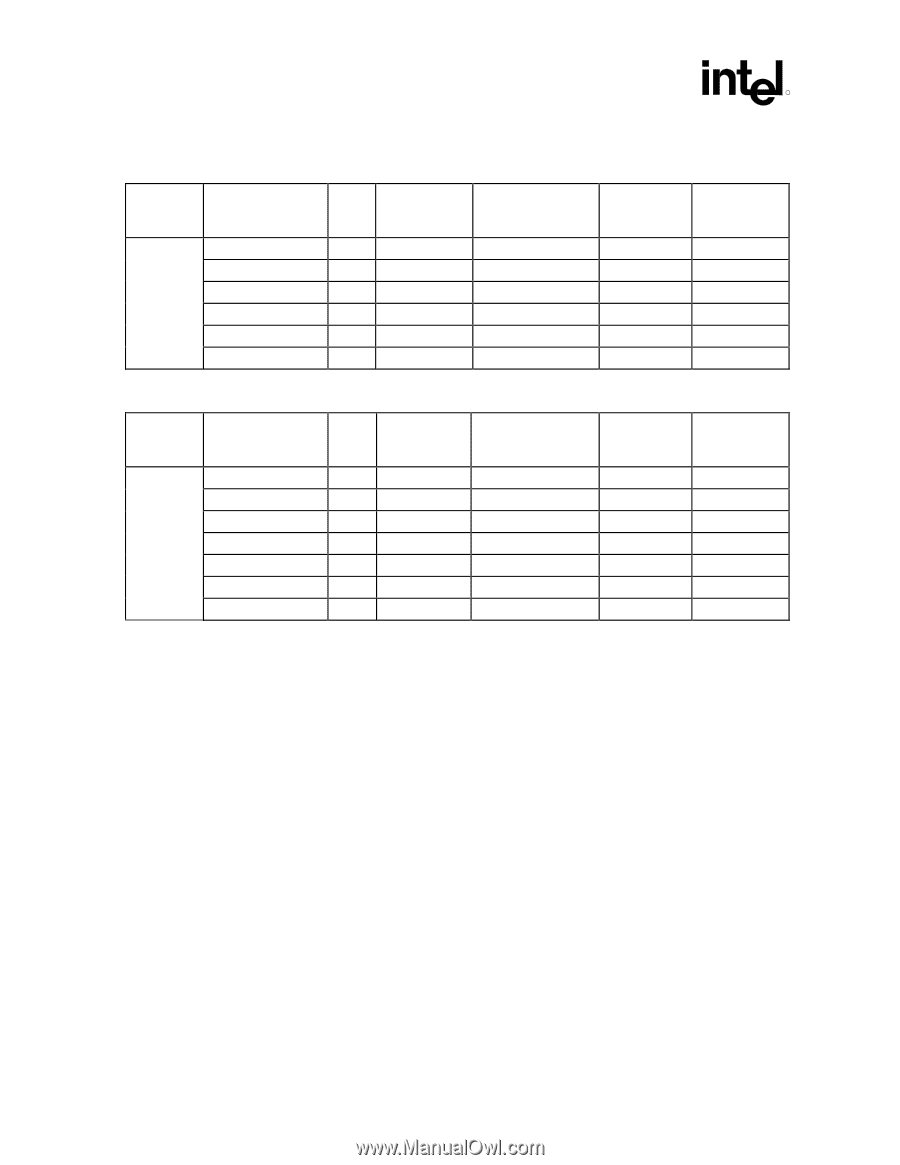

Signal Description R Table 2-5. Clocking Reset and S3 States Interface Signal Name Clocks HCLKN HCLKP GCLKN GCLKP DREFCLKN DREFCLKP State During I/O RSTIN# Assertion I IN I IN I IN I IN I IN I IN State After RSTIN# Deassertion IN IN IN IN IN IN Table 2-6. Miscellaneous Reset and S3 States Interface Signal Name Misc. RSTIN# PWROK EXTTS# BSEL[2:0] MTYPE EXP_SLR ICH_SYNC# I/O State During RSTIN# Assertion State After RSTIN# De-assertion I IN I HV I PU I TRI I TERM HV I TERM HV O PU IN HV PU TRI TERM HV TERM HV PU § S3 IN IN IN IN IN IN S3 IN HV PU TRI TERM HV TERM HV PU Pull-up/ Pull-down Pull-up/ Pull-down 34 Intel® 82925X/82925XE MCH Datasheet

Signal Description

R

34

Intel

®

82925X/82925XE MCH Datasheet

Table 2-5. Clocking Reset and S3 States

Interface

Signal Name

I/O

State During

RSTIN#

Assertion

State After

RSTIN# De-

assertion

S3

Pull-up/

Pull-down

HCLKN

I

IN

IN

IN

HCLKP

I

IN

IN

IN

GCLKN

I

IN

IN

IN

GCLKP

I

IN

IN

IN

DREFCLKN

I

IN

IN

IN

Clocks

DREFCLKP

I

IN

IN

IN

Table 2-6. Miscellaneous Reset and S3 States

Interface

Signal Name

I/O

State During

RSTIN#

Assertion

State After RSTIN#

De-assertion

S3

Pull-up/

Pull-down

RSTIN#

I

IN

IN

IN

PWROK

I

HV

HV

HV

EXTTS#

I

PU

PU

PU

BSEL[2:0]

I

TRI

TRI

TRI

MTYPE

I

TERM HV

TERM HV

TERM HV

EXP_SLR

I

TERM HV

TERM HV

TERM HV

Misc.

ICH_SYNC#

O

PU

PU

PU

§