Intel 925 Data Sheet - Page 173

Functional Description - pentium

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

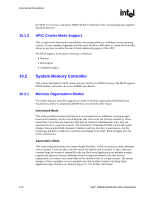

Page 173 highlights

Functional Description R 10 Functional Description 10.1 10.1.1 10.1.2 This chapter describes the MCH interfaces and major functional units. Host Interface The MCH supports the Pentium 4 processor subset of the Enhanced Mode Scaleable Bus. The cache line size is 64 bytes. Source synchronous transfer is used for the address and data signals. The address signals are double pumped, and a new address can be generated every other bus clock. When the 82925X MCH bus clock runs at 200 MHz, the address signals run at 400 MT/s for a maximum address queue rate of 66/100 million addresses/sec. The data is quad pumped and an entire 64 byte cache line can be transferred in two bus clocks. With a bus clock of 200 MHz, the data signals run at 800 MT/s for a maximum bandwidth of 6.4 GB/s. When the 82925XE MCH bus clock runs at 266 MHz, the address signals run at 533 MT/s for a maximum queue rate of 88/133 million addresses/sec. With a 82925XE bus clock at 266 MHz, the data signals run at 1066 MT/s for a maximum bandwidth of 8.5 GB/s. The FSB interface supports up to 12 simultaneous outstanding transactions. The MCH supports only one outstanding deferred transaction on the FSB. FSB GTL+ Termination The MCH integrates GTL+ termination resistors on die. Also, approximately 2.8 pf (fast) - 3.3 pf (slow) per pad of on die capacitance will be implemented to provide better FSB electrical performance. FSB Dynamic Bus Inversion The MCH supports Dynamic Bus Inversion (DBI) when driving and when receiving data from the processor. DBI limits the number of data signals that are driven to a low voltage on each quad pumped data phase. This decreases the worst-case power consumption of the MCH. HDINV[3:0]# indicate if the corresponding 16 bits of data are inverted on the bus for each quad pumped data phase: HDINV[3:0]# HDINV0# HDINV1# HDINV2# HDINV3# Data Bits HD[15:0]# HD[31:16]# HD[47:32]# HD[63:48]# When the processor or the MCH drives data, each 16-bit segment is analyzed. If more than 8 of the 16 signals would normally be driven low on the bus, the corresponding HDINV# signal will be asserted and the data will be inverted prior to being driven on the bus. When the processor or Intel® 82925X/82925XE MCH Datasheet 173