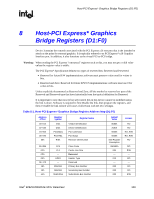

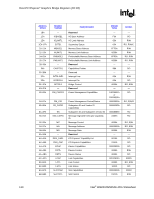

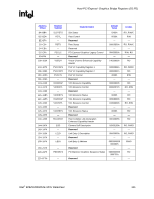

Intel 925 Data Sheet - Page 107

DMILCTL-DMI Link Control, DMILSTS-DMI Link Status

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

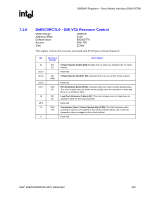

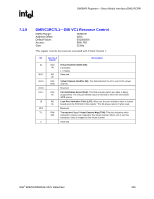

Page 107 highlights

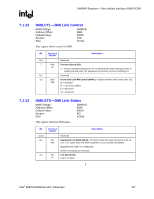

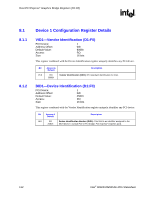

DMIBAR Registers-Direct Media Interface (DMI) RCRB R 7.1.12 DMILCTL-DMI Link Control MMIO Range: Address Offset: Default Value: Access: Size: DMIBAR 088h 0000h R/W 16 bits This register allows control of DMI. Bit Access & Default Description 15:8 Reserved 7 R/W Extended Synch (ES): 0h 1 = Forces extended transmission of FTS ordered sets when exiting L0s prior to entering L0 and extra TS1 sequences at exit from L1 prior to entering L0. 6:2 Reserved 1:0 R/W Active State Link PM Control (APMC): Indicates whether DMI should enter L0s. 00b 00 = Disabled 01 = L0s entry enabled 10 = Reserved 11 = Reserved 7.1.13 DMILSTS-DMI Link Status MMIO Range: Address Offset: Default Value: Access: Size: DMIBAR 08Ah 0001h RO 16 bits This register indicates DMI status. Bit 15:10 9:4 3:0 Access & Default Description Reserved RO Negotiated Link Width (NLW): This field is valid only when the link is in the L0, 00h L0s, or L1 states (after link width negotiation is successfully completed). Negotiated link width is x4 (000100b). All other encodings are reserved. RO Link Speed (LS) 1h Link is 2.5 Gb/s. § Intel® 82925X/82925XE MCH Datasheet 107