Intel 925 Data Sheet - Page 86

C0DRT1-Channel A DRAM Timing Register, MMIO Range, MCHBAR, Address Offset, Default Value, Access, R/W

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 86 highlights

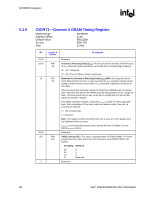

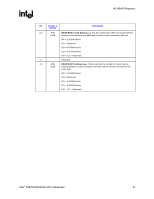

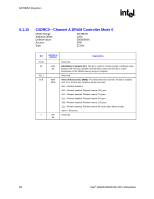

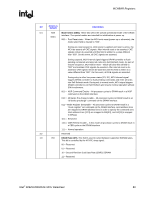

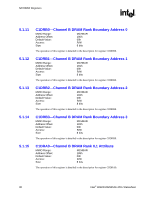

MCHBAR Registers R 5.1.9 C0DRT1-Channel A DRAM Timing Register MMIO Range: Address Offset: Default Value: Access: Size: MCHBAR 114h 900122hh R/W, RO 32 bits Bit 31:24 23:20 19 18:10 9:8 7 Access & Default R/W 9h RO 0b R/W 01b Description Reserved Activate to Precharge delay (tRAS). This bit controls the number of DRAM clocks for tRAS. Minimum recommendations are beside their corresponding encodings. 0h - 3h = Reserved 4h - Fh = Four to Fifteen Clocks respectively. Reserved for Activate to Precharge Delay (tRAS) MAX: It is required that the Panic Refresh timer be set to a value less than the tRAS maximum. Based on this setting, a Panic Refresh occurs before TRAS maximum expiration and closes all the banks. This bit controls the maximum number of clocks that a DRAM bank can remain open. After this time period, the DRAM controller will guarantee to pre-charge the bank. This time period may or may not be set to overlap with time period that requires a refresh to happen. The DRAM controller includes a separate tRAS-MAX counter for every supported bank. With a maximum of four ranks, and four banks per rank, there are 16 counters per channel. 0 = 120 microseconds 1 = Reserved Note: This register will become Read Only with a value of 0 if the design does not implement these counters. tRAS-MAX is not required because a panic refresh will close all banks in a rank before tRAS-MAX expires. Reserved CASB Latency (tCL). This value is programmable on DDR2 DIMMs. The value programmed here must match the CAS Latency of every DDR2 DIMM in the system. Encoding DDR2 CL 00 5 01 4 10 3 11 Reserved Reserved 86 Intel® 82925X/82925XE MCH Datasheet