Intel 925 Data Sheet - Page 164

APIC Configuration Space FEC0_0000h-FECF_FFFFh, PCI Memory Address Range - express chipset

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

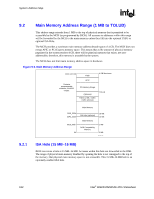

Page 164 highlights

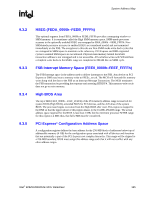

System Address Map R Figure 9-4. PCI Memory Address Range FFFF_FFFFh FFE0_0000h FEF0_0000h FEE0_0000h FED0_0000h FEC8_0000h FEC0_0000h High BIOS DMI Interface (subtractively decode) FSB Interrupts DMI Interface (subtractively decode) Local (processor) APIC I/O APIC DMI Interface (subtractively decode) 4 GB 4 GB - 2 MB 4 GB - 17 MB 4 GB - 18 MB 4 GB - 19 MB 4 GB - 20 MB Optional HSEG FEDA_0000h to FEDB_FFFFh F000_0000h PCI Express Configuration Space 4 GB - 256 MB Possible address range (Not guaranteed) E000_0000h DMI Interface (subtractively decode) 4 GB - 512 MB Programmable windows, graphics ranges, PCI Express* Port could be here TOLUD PCI_Address_Ranges_G-P-only 9.3.1 APIC Configuration Space (FEC0_0000h-FECF_FFFFh) This range is reserved for APIC configuration space. The I/O APIC(s) usually reside in the ICH6 portion of the chipset, but may also exist as stand-alone components. The IOAPIC spaces are used to communicate with IOAPIC interrupt controllers that may be populated in the system. Since it is difficult to relocate an interrupt controller using plug-and-play software, fixed address decode regions have been allocated for them. Processor accesses to the default IOAPIC region (FEC0_0000h to FEC7_FFFFh) are always forwarded to DMI. 164 Intel® 82925X/82925XE MCH Datasheet