Intel 925 Data Sheet - Page 114

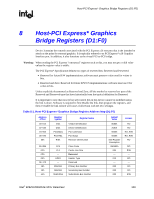

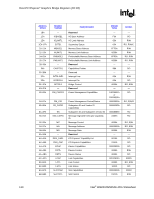

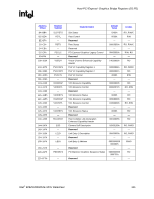

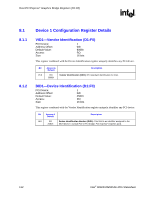

PCISTS1-PCI Status D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 114 highlights

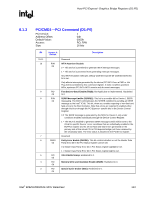

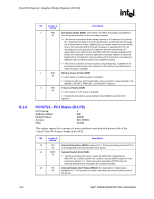

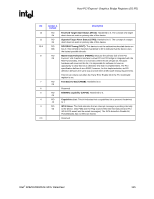

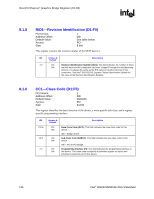

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.4 Bit Access & Default Description 2 R/W Bus Master Enable (BME): This bit does not affect forwarding of completions 0b from the primary interface to the secondary interface. 0 = This device is prevented from making memory or I/O requests to its primary bus. Note that according to the PCI specification, as MSI interrupt messages are in-band memory writes, disabling the bus master enable bit prevents this device from generating MSI interrupt messages or passing them from its secondary bus to its primary bus. Upstream memory writes/reads, I/O writes/reads, peer writes/reads, and MSIs will all be treated as illegal cycles. Writes are forwarded to memory address 0h with byte enables de-asserted. Reads will be forwarded to memory address 0h and will return Unsupported Request status (or Master abort) in its completion packet. 1 = This device is allowed to issue requests to its primary bus. Completions for previously issued memory read requests on the primary bus will be issued when the data is available. 1 R/W Memory Access Enable (MAE) 0b 0 = All of device 1's memory space is disabled. 1 = Enable the Memory and Pre-fetchable memory address ranges defined in the MBASE1, MLIMIT1, PMBASE1, and PMLIMIT1 registers. 0 R/W IO Access Enable (IOAE) 0b 0 = All of device 1's I/O space is disabled. 1 = Enable the I/O address range defined in the IOBASE1 and IOLIMIT1 registers. PCISTS1-PCI Status (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 06h 0000h RO, R/W/C 16 bits This register reports the occurrence of error conditions associated with primary side of the "virtual" Host-PCI Express bridge in the MCH. Bit Access & Default Description 15 RO Detected Parity Error (DPE): Hardwired to 0. Parity (generating poisoned TLPs) 0b is not supported on the primary side of this device. 14 R/WC Signaled System Error (SSE): 0b 1 = This bit is set when this Device sends an SERR due to detecting an ERR_FATAL or ERR_NONFATAL condition and the SERR Enable bit in the Command register is '1'. Both received (if enabled by BCTRL1[1]) and internally detected error messages do not affect this field. 13 RO Received Master Abort Status (RMAS): Not Applicable or Implemented. 0b Hardwired to 0. The concept of a master abort does not exist on primary side of this device. 114 Intel® 82925X/82925XE MCH Datasheet