Intel 925 Data Sheet - Page 136

DCTL-Device Control D1:F0, ERR_NONFATAL

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 136 highlights

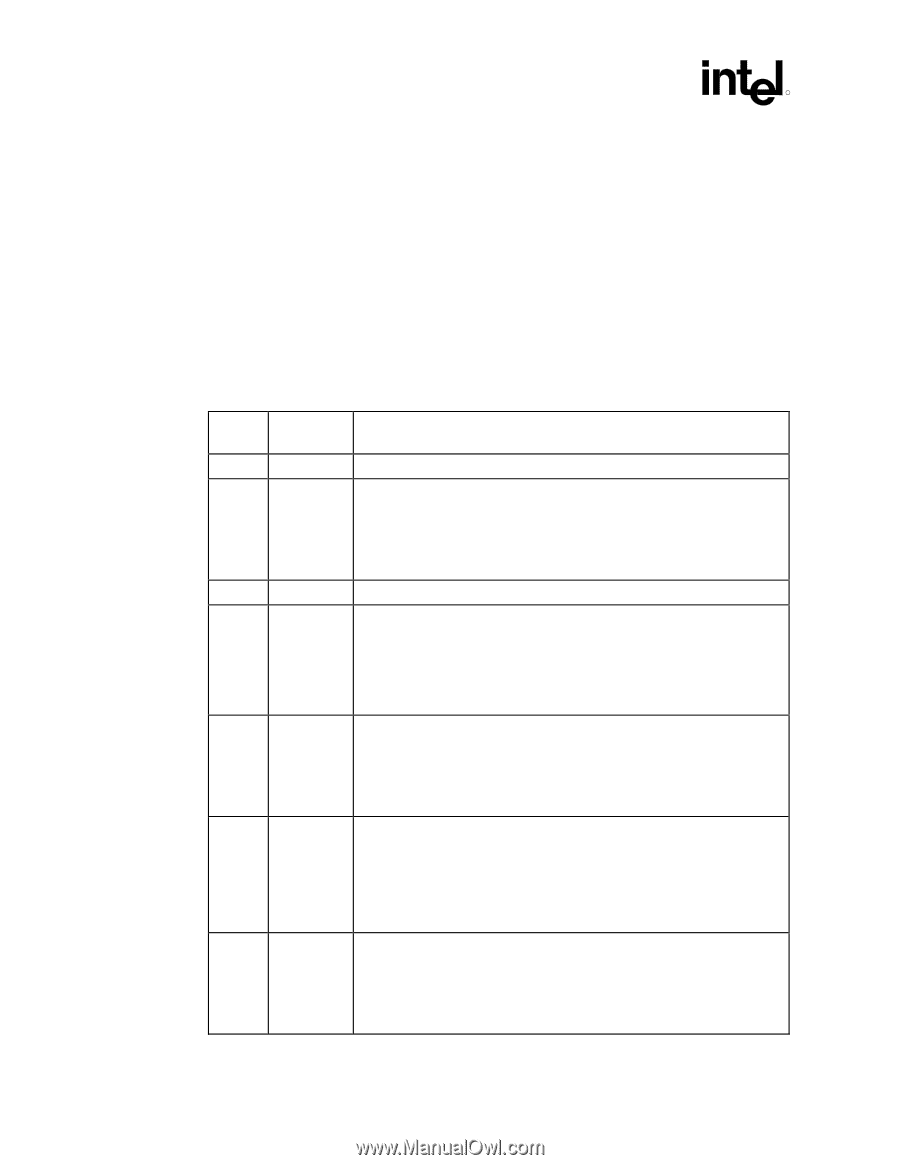

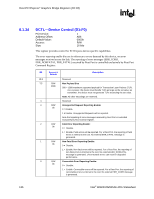

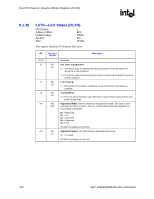

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.34 DCTL-Device Control (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 A8h 0000h R/W 16 bits This register provides control for PCI Express device specific capabilities. The error reporting enable bits are in reference to errors detected by this device, not error messages received across the link. The reporting of error messages (ERR_CORR, ERR_NONFATAL, ERR_FATAL) received by Root Port is controlled exclusively by Root Port Command Register. Bit Access & Default Description 15:8 Reserved 7:5 R/W Max Payload Size 000b 000 = 128B maximum supported payload for Transaction Layer Packets (TLP). As a receiver, the device must handle TLPs as large as the set value; as transmitter, the device must not generate TLPs exceeding the set value. Note: All other encodings are reserved. 4 Reserved 3 R/W Unsupported Request Reporting Enable: 0b 0 = Disable. 1 = Enable. Unsupported Requests will be reported. Note that reporting of error messages received by Root Port is controlled exclusively by Root Control register. 2 R/W Fatal Error Reporting Enable: 0b 0 = Disable. 1 = Enable. Fatal errors will be reported. For a Root Port, the reporting of fatal errors is internal to the root. No external ERR_FATAL message is generated. 1 R/W Non-Fatal Error Reporting Enable: 0b 0 = Disable. 1 = Enable. Non-fatal errors will be reported. For a Root Port, the reporting of non-fatal errors is internal to the root. No external ERR_NONFATAL message is generated. Uncorrectable errors can result in degraded performance. 0 R/W Correctable Error Reporting Enable: 0b 0 = Disable. 1 = Enable. Correctable errors will be reported. For a Root Port, the reporting of correctable errors is internal to the root. No external ERR_CORR message is generated. 136 Intel® 82925X/82925XE MCH Datasheet