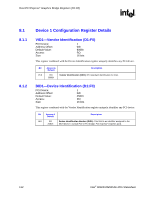

Intel 925 Data Sheet - Page 115

Received Target Abort Status RTAS, Master Data Parity Error PMDPE

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

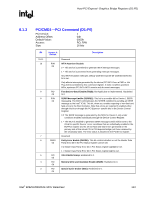

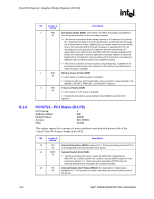

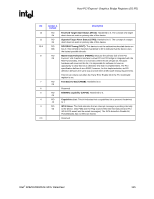

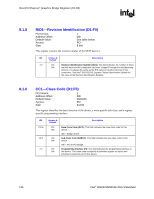

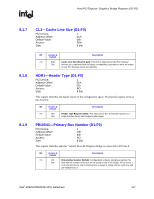

Page 115 highlights

Host-PCI Express* Graphics Bridge Registers (D1:F0) R Bit Access & Default Description 12 RO Received Target Abort Status (RTAS): Hardwired to 0. The concept of a target 0b abort does not exist on primary side of this device. 11 RO Signaled Target Abort Status (STAS): Hardwired to 0. The concept of a target 0b abort does not exist on primary side of this device. 10:9 RO DEVSELB Timing (DEVT): This device is not the subtractive decoded device on 00b bus 0. This bit field is therefore hardwired to 00 to indicate that the device uses the fastest possible decode. 8 RO Master Data Parity Error (PMDPE): Because the primary side of the PCI 0b Express* x16 Graphics Interface's virtual PCI-to-PCI bridge is integrated with the MCH functionality, there is no scenario where this bit will get set. Because hardware will never set this bit, it is impossible for software to have an opportunity to clear this bit or otherwise test that it is implemented. The PCI specification defines it as a R/WC; however, for this implementation, an RO definition behaves the same way and will meet all Microsoft testing requirements. This bit can only be set when the Parity Error Enable bit in the PCI Command register is set. 7 RO Fast Back-to-Back (FB2B): Hardwired to 0. 0b 6 Reserved 5 RO 66/60MHz capability (CAP66): Hardwired to 0. 0b 4 RO Capabilities List: This bit indicates that a capabilities list is present. Hardwired 1b to 1. 3 RO INTA Status: This field indicates that an interrupt message is pending internally 0b to the device. Only PME and Hot Plug sources feed into this status bit (not PCI INTA-INTD assert and de-assert messages). The INTA Assertion Disable bit, PCICMD1[10], has no effect on this bit. 2:0 Reserved Intel® 82925X/82925XE MCH Datasheet 115