Intel 925 Data Sheet - Page 30

Power and Ground, Reset States and Pull-up/Pull-downs, Legend

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 30 highlights

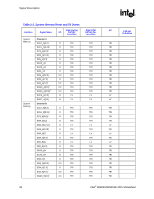

Signal Description R 2.8 2.9 Power and Ground Name VCC VTT VCC_EXP VCCSM VCC2 VCCA_EXPPLL VCCA_HPLL VCCA_SMPLL VSS Voltage 1.5 V 1.2 V 1.5 V 1.8 V 2.5 V 1.5 V 1.5 V 1.5 V 0 V Description Core Power. Processor System Bus Power. PCI Express* and DMI Power. System Memory Power. DDR2: VCCSM = 1.8 V (VCCSM = 1.9 V for DDR2 533 CAS 3-3-3) 2.5 V CMOS Power. PCI Express PLL Analog Power. Host PLL Analog Power. System Memory PLL Analog Power. Ground. Reset States and Pull-up/Pull-downs This section describes the expected states of the MCH I/O buffers during and immediately after the assertion of RSTIN#. This table only refers to the contributions on the interface from the MCH and does not reflect any external influence (such as external pull-up/pull-down resistors or external drivers). Legend: CMCT: DRIVE: TERM: LV: HV: IN: ISO: TRI: PU: PD: STRAP: Common Mode Center Tapped. Differential signals are weakly driven to the common mode central voltage. Strong drive (to normal value supplied by core logic if not otherwise stated) Normal termination devices are turned on Low voltage High voltage Input buffer enabled Isolate input buffer so that it does not oscillate if input left floating Tri-state Weak internal pull-up Weak internal pull-down Strap input sampled during assertion or on the de-asserting edge of RSTIN# 30 Intel® 82925X/82925XE MCH Datasheet