Intel 925 Data Sheet - Page 109

Host-PCI Express* Graphics Bridge Registers (D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

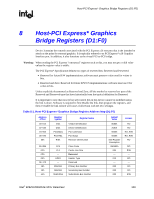

Page 109 highlights

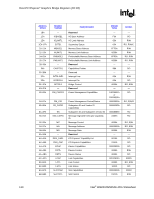

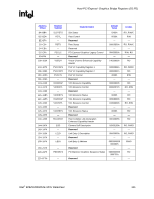

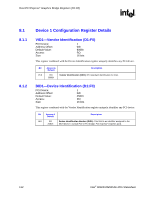

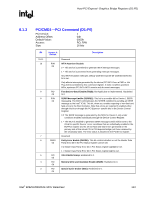

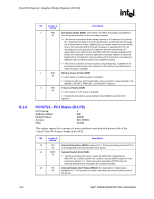

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8 Host-PCI Express* Graphics Bridge Registers (D1:F0) Device 1contains the controls associated with the PCI Express x16 root port that is the intended to attach as the point for external graphics. It is typically referred to as PCI Express* x16 Graphics Interface port. In addition, it also functions as the virtual PCI-to-PCI bridge. Warning: When reading the PCI Express "conceptual" registers such as this, you may not get a valid value unless the register value is stable. The PCI Express* Specification defines two types of reserved bits: Reserved and Preserved: • Reserved for future R/W implementations; software must preserve value read for writes to bits. • Reserved and Zero: Reserved for future R/WC/S implementations; software must use 0 for writes to bits. Unless explicitly documented as Reserved and Zero, all bits marked as reserved are part of the Reserved and Preserved type that have historically been the typical definition for Reserved. It is important to note that most (if not all) control bits in this device cannot be modified unless the link is down. Software is required to first Disable the link, then program the registers, and then re-enable the link (which will cause a full-retrain with the new settings). Table 8-1. Host-PCI Express* Graphics Bridge Register Address Map (D1:F0) Address Offset 00-01h 02-03h 04-05h 06-07h 08h 09-0Bh 0Ch 0Dh 0Eh 0F-17h 18h 19h 1Ah Register Symbol VID1 DID1 PCICMD1 PCISTS1 RID1 CC1 CL1 - HDR1 - PBUSN1 SBUSN1 SUBUSN1 Register Name Vendor Identification Device Identification PCI Command PCI Status Revision Identification Class Code Cache Line Size Reserved Header Type Reserved Primary Bus Number Secondary Bus Number Subordinate Bus Number Default Value 8086h 2581h 0000h 0000h See Register Description 060400h 00h - 01h - 00h 00h 00h Access RO RO RO, R/W RO, R/W RO RO R/W - RO - RO RO R/W Intel® 82925X/82925XE MCH Datasheet 109