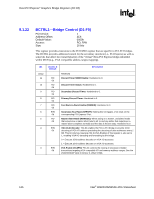

Intel 925 Data Sheet - Page 129

PM_CS1-Power Management Control/Status, D1:F0, PCI Device, Address Offset, Default Value, Access, RO

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 129 highlights

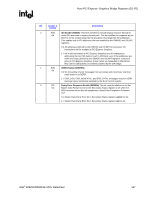

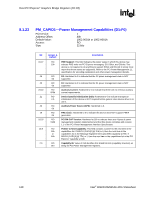

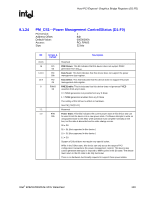

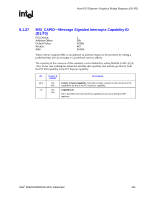

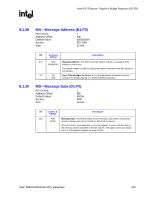

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.24 PM_CS1-Power Management Control/Status (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 84h 00000000h RO, R/W/S 32 bits Bit 31:16 15 14:13 12:9 8 7:2 1:0 Access & Default RO 0b RO 00b RO 0h R/W/S 0b R/W 00b Description Reserved PME Status: This bit indicates that this device does not support PME# generation from D3cold. Data Scale: This field indicates that this device does not support the power management data register. Data Select: This field indicates that this device does not support the power management data register. PME Enable: This bit indicates that this device does not generate PMEB assertion from any D-state. 0 = PMEB generation not possible from any D State 1 = PMEB generation enabled from any D State The setting of this bit has no effect on hardware. See PM_CAP[15:11] Reserved Power State: This field indicates the current power state of this device and can be used to set the device into a new power state. If software attempts to write an unsupported state to this field, write operation must complete normally on the bus, but the data is discarded and no state change occurs. 00 = D0 01 = D1 (Not supported in this device.) 10 = D2 (Not supported in this device.) 11 = D3 Support of D3cold does not require any special action. While in the D3hot state, this device can only act as the target of PCI configuration transactions (for power management control). This device also cannot generate interrupts or respond to MMR cycles in the D3 state. The device must return to the D0 state to be fully functional. There is no hardware functionality required to support these power states. Intel® 82925X/82925XE MCH Datasheet 129